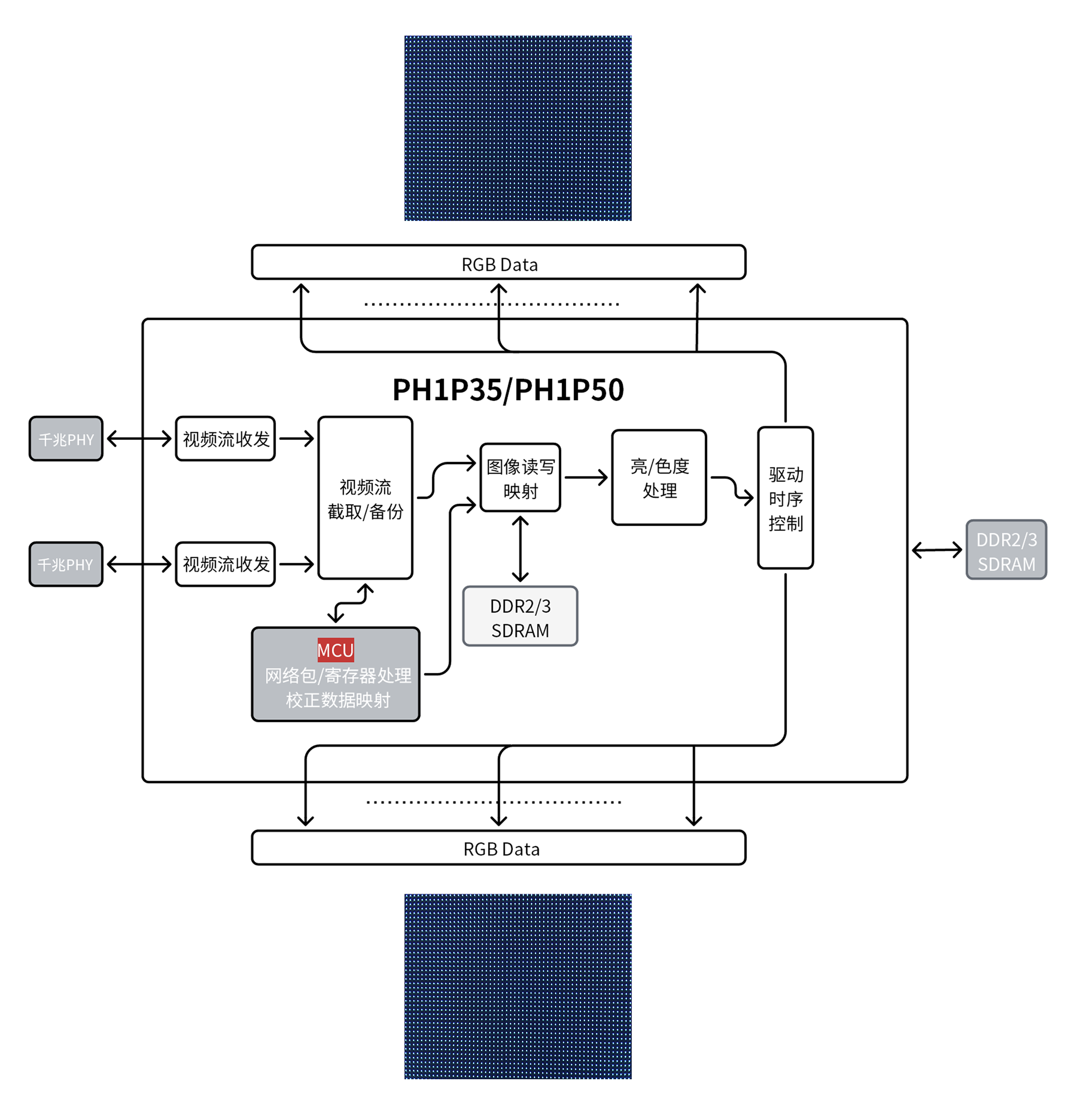

高性能LED通用接收卡

基于安路科技FPGA的LED显示屏驱动系统,通过千兆以太网或高速数据接口,进行视频数据的传输,让单张卡能带载更大面积。客户可以通过器件内部丰富的逻辑资源实现更多样化视频数据处理、点阵驱动算法等。安路科技PH1P35,PH1P50系列提供内置MCU硬核、以及DDR内存,可以让通信协议操作更简单,校正数据处理更高效。解放FPGA逻辑资源,实现更多驱动支持与图像数据处理。

FPGA技术架构优势

▸ FPGA电平标准丰富,构建1G、5Gbps等高速网络传输链路系统

▸ MCU可以实现协议与数据解析和处理,校正数据管理以及其他智能控制,通过总线与MUC与逻辑的智能交互,减少了FPGA逻辑资源开销与后期维护时间,让系统可实现更多显示功能。

▸ PH1P50系列的SERDES,可以实现高速带宽需求,SERDES 单Lane可输出5~10Gbps/s数据。同时4 Lane SERDES可以连接DP/HDMI高清接口,实现视频直连的高性价方案。

▸ FPGA内集成DDR内存,带宽可支持6.4~8.5GB,该存储可实现图像与校正数据缓存,单芯片方案显著降低能耗,提升存储带宽与客户PCB BOM成本,减少开发时间。

▸ FPGA Dual Boot启动方案,让接收卡支持更多功能,实现恒流源与PWM驱动高清画质数据驱动

▸ 16bit~20bit灰度控制精度,支持3840Hz以上超高频刷新(手机拍摄无频闪体验)

▸ 动态可编程伽马校正

▸ 联动LED自动校准系统,自动补偿LED衰减曲线

▸ LED显示屏显示效果与驱动芯片的增加扩展,使用FPGA可编程逻辑资源,功能无限重构与叠代

▸ 零延迟响应:从FPGA接收视频信号输入到LED输出延迟,在系统上实现多个卡实现同步显示

▸ 故障自愈:可对屏幕的坏点进行循环检测

PH1P实现的LED方案,内部支持更大的图像数据缓存,集成了MCU与高速接口,将FPGA的硬件可编程优势与LED显示处理深度融合,不仅实现像素级的精准控制,更能实现高效能的随心智能控制。特别适合高密度小间距、会议一体机、电影屏等高端LED显示屏应用场景。

通过PH1P FPGA器件系列,可降低客户BOM与开发成本,在降低能耗的同时,让每个LED单元都成为艺术表达的智能像素点。